Next: SSA in buffers

Up: Reducing Spurious Switching Activity

Previous: Overhead for gating

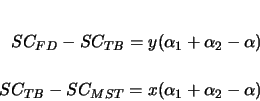

Three output network topologies were introduced in

Section III. If all the output data are sent to all

the receivers without regard to whether they need the data or not,

the MST output network will consume the least power and the fully

dedicated the most. If interconnect SSA is suppressed using the

proposed techniques, however, this will not always be true.

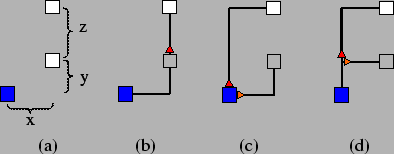

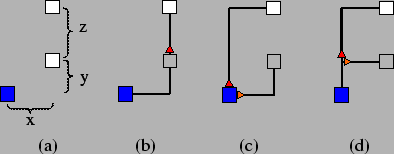

Fig. 10 shows a DPU, colored black, sending

data to two other DPUs, colored white, using different output

network topologies. It also shows the optimal locations for gating

signals with SSA as small triangles.

Figure 10:

Different output network topologies for

(a) one DPU sending data to two other

DPUs:

(b) MST,

(c) fully dedicated, and

(d) trunk-branches.

|

Suppose tri-state buffers are used so that the last useful value

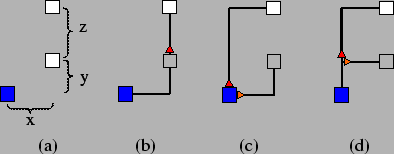

is remembered in the gated idle cycles. Let  denote the

unit-length switched capacitance for data, say, for variables

denote the

unit-length switched capacitance for data, say, for variables

, needed by the upper receiver, which is estimated as

, needed by the upper receiver, which is estimated as

where

is the unit-length switched capacitance in

the wire when

is the unit-length switched capacitance in

the wire when  is followed by

is followed by  . That for the lower

receiver,

. That for the lower

receiver,  , and that for all the output variables of the

sender,

, and that for all the output variables of the

sender,  , can be estimated in the same way. Assuming

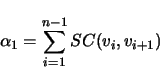

signal gating is performed at the optimal locations shown in

Fig. 10, we can estimate the total wire

switched capacitance for the output network implemented as

follows: MST,

, can be estimated in the same way. Assuming

signal gating is performed at the optimal locations shown in

Fig. 10, we can estimate the total wire

switched capacitance for the output network implemented as

follows: MST,  , fully dedicated,

, fully dedicated,  , and

trunk-branches,

, and

trunk-branches,  , as

, as

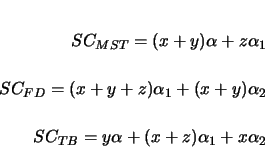

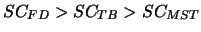

The above equations imply that

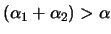

Therefore, when

, we have

, we have

and when

and when

,

,

.

Since

.

Since

can be either larger or

smaller than

can be either larger or

smaller than  , none of these topologies

is always better than the others in terms of power

consumption. In this work, the trunk-branches topology

is assumed due to its never-the-worst power consumption

and the algorithmic simplicity for constructing it.

, none of these topologies

is always better than the others in terms of power

consumption. In this work, the trunk-branches topology

is assumed due to its never-the-worst power consumption

and the algorithmic simplicity for constructing it.

Next: SSA in buffers

Up: Reducing Spurious Switching Activity

Previous: Overhead for gating

Lin Zhong

2003-10-11